Mastering SystemVerilog assertion variable delay is crucial for efficient verification of digital designs. By understanding the nuances of variable delay, engineers can create more effective and robust assertions that help identify potential issues early in the design cycle. In this article, we'll delve into the world of SystemVerilog assertions and explore five ways to master variable delay.

Understanding SystemVerilog Assertions

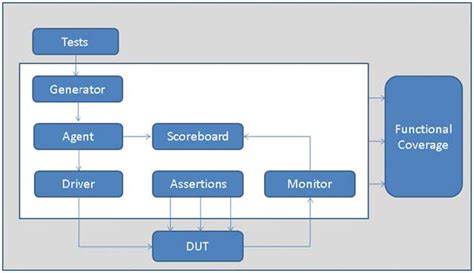

SystemVerilog assertions are a powerful tool for verifying digital designs. They allow engineers to specify expected behavior and detect potential issues, ensuring that the design functions as intended. Assertions can be used to verify various aspects of a design, including timing, protocol compliance, and functional correctness.

What is Variable Delay?

Variable delay refers to the ability of SystemVerilog assertions to accommodate varying delay times between signal transitions. This feature is essential in modern digital designs, where delays can vary depending on factors such as process, voltage, and temperature (PVT). By using variable delay, engineers can create assertions that are more robust and flexible, allowing them to account for these variations.

5 Ways to Master SystemVerilog Assertion Variable Delay

1. Using the delay Keyword

The delay keyword is used to specify a fixed delay between signal transitions. However, when dealing with variable delay, it's essential to use the delay keyword in conjunction with the <= operator. This allows the assertion to accommodate delays up to a specified value.

Example:

assert property (@posedge clk) a |=> delay(3) b;

In this example, the assertion checks that signal b is asserted within 3 clock cycles after signal a is asserted.

2. Utilizing the ## Operator

The ## operator is used to specify a range of delays between signal transitions. This operator is particularly useful when dealing with variable delay, as it allows engineers to specify a minimum and maximum delay value.

Example:

assert property (@posedge clk) a |=> ##[2:5] b;

In this example, the assertion checks that signal b is asserted between 2 and 5 clock cycles after signal a is asserted.

3. Employing the >= Operator

The >= operator is used to specify a minimum delay between signal transitions. This operator is useful when dealing with variable delay, as it allows engineers to ensure that a minimum delay is met.

Example:

assert property (@posedge clk) a |=> delay(2) >= b;

In this example, the assertion checks that signal b is asserted at least 2 clock cycles after signal a is asserted.

4. Using the <= Operator

The <= operator is used to specify a maximum delay between signal transitions. This operator is useful when dealing with variable delay, as it allows engineers to ensure that a maximum delay is not exceeded.

Example:

assert property (@posedge clk) a |=> delay(5) <= b;

In this example, the assertion checks that signal b is asserted within 5 clock cycles after signal a is asserted.

5. Combining Operators

SystemVerilog assertions allow engineers to combine operators to create more complex variable delay specifications. By combining the delay, ##, >=, and <= operators, engineers can create assertions that accommodate a wide range of delay variations.

Example:

assert property (@posedge clk) a |=> delay(2) >= ##[2:5] b;

In this example, the assertion checks that signal b is asserted between 2 and 5 clock cycles after signal a is asserted, with a minimum delay of 2 clock cycles.

Gallery of SystemVerilog Assertion Variable Delay Examples

Frequently Asked Questions

What is SystemVerilog assertion variable delay?

+SystemVerilog assertion variable delay refers to the ability of SystemVerilog assertions to accommodate varying delay times between signal transitions.

How do I use the `delay` keyword in SystemVerilog assertions?

+The `delay` keyword is used to specify a fixed delay between signal transitions. It can be used in conjunction with the `<=` operator to accommodate variable delay.

What is the purpose of the `##` operator in SystemVerilog assertions?

+The `##` operator is used to specify a range of delays between signal transitions. It is particularly useful when dealing with variable delay.

We hope this article has provided you with a comprehensive understanding of SystemVerilog assertion variable delay. By mastering this concept, you can create more effective and robust assertions that help identify potential issues early in the design cycle. If you have any questions or need further clarification, please don't hesitate to ask.